Cadence Custom Ic Design Crackers

Cadence Design Systems, Inc. In addition, it offers custom IC design and verification products to create schematic and physical representations of circuits down to the transistor level. Easily share your publications and get them in front of Issuu. Title: Winfield community assessment report DRAFT, Author: Teska Associates,. Dec 12, 2017. OxFORD Asset Management LLP grew its stake in Cadence Design Systems, Inc. (NASDAQ:CDNS) by 12.0% in the 3rd quarter, according to its most recent filing with the SEC. The firm owned 221773 shares of the software maker's stock after buying an additional 23694 shares during the quarter.

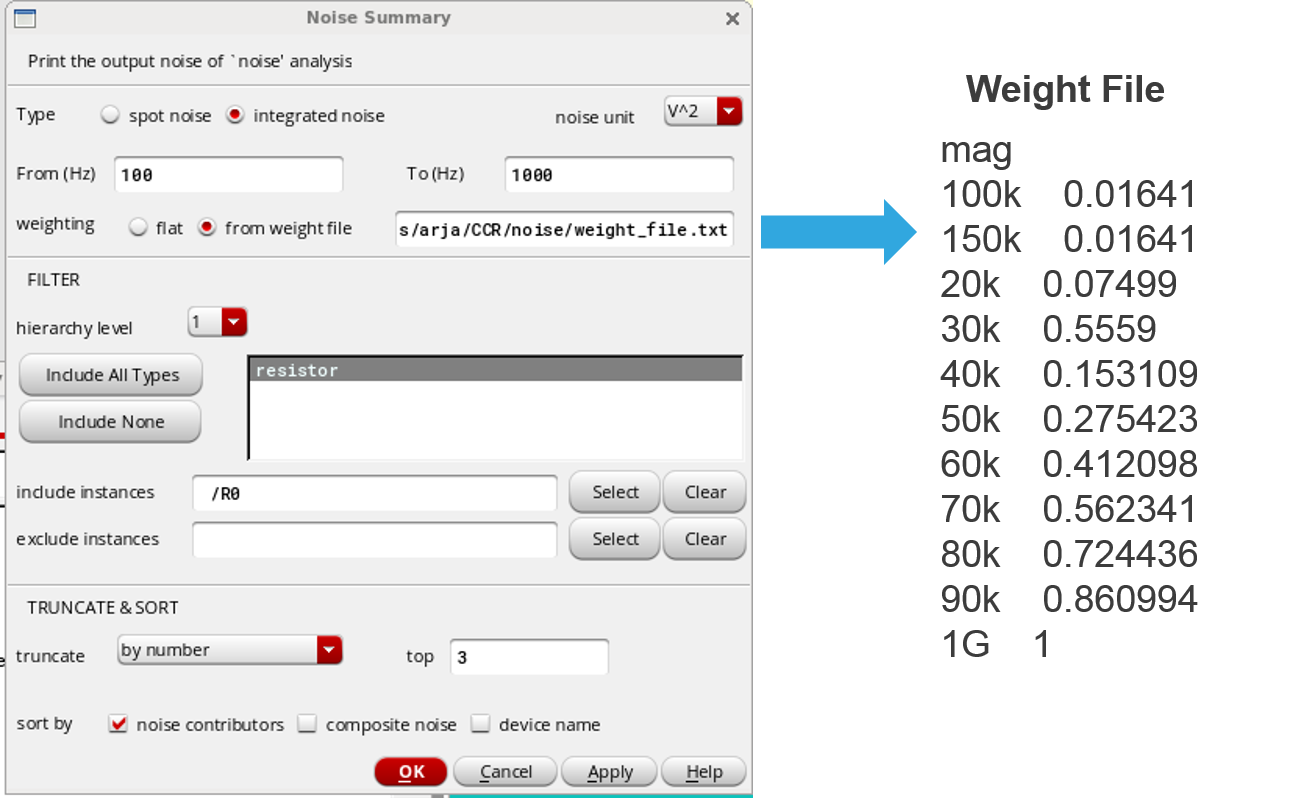

Semiwiki.com SemiWiki.com - 20nm IC Design at IBM using Cadence Tools 1205 × 697 - 76k - jpg eetimes.com Cadence rolls custom- IC tools into one platform EE Times 503 × 331 - 26k - gif cadence.com Custom IC / Analog / RF Design 600 × 299 - 37k - png community.cadence.com The Art of Analog Design Part 6: Response to Frank's Question to. 416 × 721 - 82k - png community.cadence.com The Art of Analog Design Part 4: Mismatch Analysis - Custom IC. 1208 × 614 - 38k - png community.cadence.com Any Idea to Disable Pins Display in Layout L? - Custom IC Design. 1024 × 640 - 418k - jpg community.cadence.com How do you annotate region of operation for NMOS transistors in. 2160 × 1440 - 421k - png community.cadence.com Adding Weighted Noise Via Calculator Custom Function - Custom IC. 1304 × 798 - 207k - png community.cadence.com Virtuosity: Can I Speed up My Plots?

- Custom IC Design - Cadence. 1169 × 537 - 703k - png community.cadence.com How to use the 'gmin_check' option & set Option dc_pivot_check=yes. 1490 × 1026 - 118k - png community.cadence.com Virtuosity: Sweeping Multiple DSPF Views in ADE - Custom IC Design. 940 × 649 - 182k - jpg community.cadence.com Virtuosity: Power Filtering! - Custom IC Design - Cadence Blogs. 644 × 304 - 2976k - gif community.cadence.com Art of Analog Design Part 7: Mismatch Tuning - Custom IC Design. 1974 × 1220 - 113k - png community.cadence.com LVS mismatch - Custom IC Design - Cadence Technology Forums.

1366 × 768 - 263k - png community.cadence.com The Art of Analog Design Part 5: Mismatch Analysis II - Custom IC. 908 × 830 - 43k - png eda360insider.wordpres. EDA360 Insider The Way Forward for Electronic Design by Steve. 560 × 437 - 55k - jpg eda360insider.wordpres.

EDA360 Insider The Way Forward for Electronic Design by Steve. 420 × 437 - 25k - jpg electronicdesign.com Free Downloadable Spice Tools Capture And Simulate Analog Circuits. 600 × 300 - 29k - jpg eda360insider.wordpres.

EDA360 Insider The Way Forward for Electronic Design by Steve. 420 × 420 - 18k - jpg eda360insider.wordpres. EDA360 Insider The Way Forward for Electronic Design by Steve. 560 × 243 - 21k - jpg.

Georgia Institute of Technology School of Electrical and Computer Engineering Cadence University Program Member Cadence Tools in the Cadence software is being used primarily in the following courses in the at: • and use version 16.6 of SPB/Orcadlite/PSpice for basic instruction in SPICE • ECE 3060 (VLSI and Advanced Digital Design): The Virtuoso schematic/layout editors along with Diva DRC/LVS tools are used by the students to design a 16bit Microprocessor. The students uses the Cadence tools to design the schematic and the layout of individual units such as Adder, Register File, Decoders, etc. And perform DRC/LVS checks on them. The Cadence tools in this course introduces students to the basic VLSI design skills. • ECE 6130/4130 (Advanced VLSI Systems): The Virtuoso schematic/layout editors and Diva/Calibre DRC/LVS/Extraction tools are used in this course to teach students advances concepts of digital system design using the NCSU Design Kit.

The course uses Cadence Virtuoso as the only acceptable tool for a semester long design project in this course. For example, in last two years in the design project students are designing a three stage pipelined system – an SRAM array, a one-cycle Interconnect, and a fast adder – using Cadence tools in this course. The design is performed at advanced technology nodes (e.g. IBM130nm, FreePDK45nm etc.) with aggressive voltage/frequency targets (~1GHZ at 0.8-1V supply). A significant number of students in this class also uses Spectre simulation environment for design while a fraction of students uses HSPICE for simulations. • (Physical Design Automation VLSI Systems): Encounter and Virtuoso for digital IC designs.

• (Analog Integrated System Design): Custom IC and Verification are utilized for projects involving deep brain stimulation, wireless cardiac monitoring and electrocardiogram monitoring. • Cadence is used for design projects in the graduate course “Wireless IC Design” (). Standard device models are used in conjunction with Spectre and SpectreRF simulation in Cadence to design circuits for Ultra Wide-Band (UWB) applications.

Baseband and time-domain simulations of analog front-ends and back-end circuits are performed. • ECE6430 (MOS Digital ICs): The MOS Digital IC course uses Virtuoso schematic/layout editor along with Spectre to teach students advanced concepts of digital circuit design. In this course, Cadence tools are normally used to solve small scale design problems in Homework. • ECE8893 (Digital System in Nanometer Nodes): In this course, each student defines his/her own design project ranging from digital system integration to low-level circuit techniques.

All the projects (~12-15) are implemented using Cadence design tools including Virtuoso, Diva or Calibre DRC/LVS/Extraction and SoC encounter (for Auto Place/Route). The designed projects may lead to Fabrication of test chips. • Cadence tools are used by the.

The goal of the team is to design digital hardware which is highly resistant to reverse engineering and attack by malicious hardware insertions (hardware Trojans). Cadence Tools in Projects Cadence software is being used in many research projects in the School of Electrical and Computer Engineering. Geniatech Usb Tv Box Software.

Canon Clc5151 Driver Windows 8. They include the following, wide-ranging initiatives. • The is designing and building prototypes, which demonstrate next generation packaging technology developed at the center.

• Integrated systems for segmented locomotion are being built in the with funding from. • The Cooperative Analog and Digital Signal Processing (CADSP) laboratory has used the Cadence tools for an intelligent audio processing project funded by National Semiconductor. Their goal is to create a low-power analog front-end that triggers a more complicated Digital Signal Processing system.

They used Cadence to simulate the individual components (filters, zero-crossings detector, and classification circuit) and the complete system. This work required them to use audio files as stimuli to analog circuits in Cadence. As a result, they created a MATLAB function,, that converts a sound file into a SPICE piece-wise-linear-source (PWLS) that can be included in a Cadence spectreS simulation, (simply by including the file under the “Environments” tab and rebuilding the netlist). They also used the ocean feature to communicate with MATLAB such that they could automatically adjust simulation parameters with a MATLAB script. • The Integrated Sensors & Systems Lab (i-SensSys) led by utilizes Cadence applications for the design and development of intergrated microsensors and their front-end signal conditioning circuitry. • The Georgia Tech Analog, Power, & Energy ICs Lab uses the Cadence tools for the simulation, layout, and verification of integrated circuits (ICs) designed, developed, built, and evaluated for the purpose of furthering their research in the field of analog, power, and energy ICs.

The files generated from the Cadence environment are used to submit IC prototypes to foundries like those supported by MOSIS. • uses Cadence in as the standard platform for IC design in SiGe technology. The tools used include icfb/msfb, layout, layout XL, schematic, hierarchy editor, diva, Assura + Assura RCX, Calibre, Spectre, Sonnet plug in, ADS Dynamic Link / rfde, GoldenGate, Encounter, Synopsys, AMS, ncverilog, and SimVision. • The supports world-class research that fosters the development and design of new communications technology in wireless/RF, wired/copper and fiber channel applications. • The lead by have taped out a 3D IC design using SOC Encounter, QRC Extraction and Virtuoso Cadence design tools and others.

The tool sets used are Custom IC and Digital IC. • The led by uses Cadence tools for virtually all of their research efforts on Digital Circuits/Systems ranging from memory design, signal processing circuits/systems, power/thermal management for multi-core design, 3D ICs design, and biomedical circuit/system design. GREEN Lab is currently using Cadence tools to tape-out a test chip in FD/SOI technology offered through MIT-Lincon Lab, GREEN lab envisions using Cadence tools (Virtuoso, Spectre, SoC Encounter, etc.) to tape out at least one test chip every year.

• The utilizes Custom IC, Verification and Allegro for projects related to neural interfacing and implantable biomedical devices. • The Yield Enhancement and Testing Research Group (YETRG) led by utilizes Allegro, SOC Encounter, QRC Extraction, RTL Compiler, Virtuoso, IUS for Custom IC and Digital IC.

Value Added Items • The assists students and research groups with learning how to use available EDA tools. • A technology library for 0.5 micron technology was created. Disclaimer Information is provided “as is” without warranty of any kind. No statement is made and no attempt has been made to examine the information, either with respect to operability, origin, authorship, or otherwise.

Please use this information at your own risk. We recommend using it on a copy of your data to be sure you understand what it does and under your conditions. Keep your master intact until you are satisfied with the use of this information within your environment. Cadence is a trademark of, Inc., 2655 Seely Avenue, San Jose, CA 95134. Questions about this page? Please contact. Last revised March 7, 2017.